STE s.a.s. ELETTRONICA TELECOMUNICAZIONI Via Maniago N.15 – 20134 – Milano – Italy Tel.: +39.02.2153524 / 2153525 / 2157891 Fax: +39.02.26410928

www.stecom.com

ste@stecom.com

#### PLL SYNTHESIZED DATA TRANSCEIVER 433.05 – 434.79 MHz ISM BAND

# **OPERATING AND SERVICE MANUAL**

## **General Description**

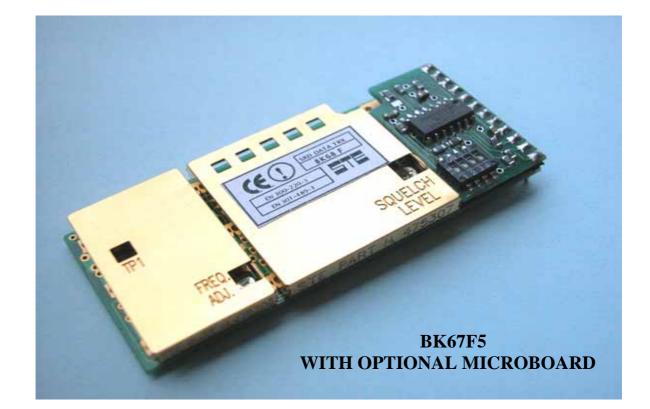

The BK67F5 is a synthesized UHF transceiver for use in wireless data transmission applications.

The transceiver operates on the 433.05 - 434.79 MHz ISM band and it is designed to comply to the European Standards EN 300-220-3 and EN 301-489-3, in accordance with the CEPT-ERC-REC 70-03 recommendation (Annex 1 – Non Specific Short Range Devices).

Together with a precision and low phase-noise crystal controlled PLL architecture, the transceiver has high reception sensitivity (-105 dBm) and high RF output power (20 mW). High RF output power allows to employ poor efficiency antennas (helical, patch, loop or a trace on a PCB) to remain under legal 10 mW ERP (Effective Radiated Power) limit.

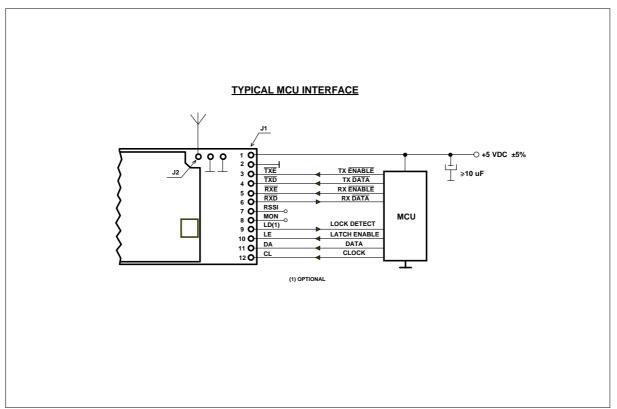

The BK67F5 is designed to be directly interfaced to a microcontroller (MCU) to control and to monitor the receive and transmit mode and to program (through a 3 wires serial interface) the appropriate Rx and Tx frequencies. In a typical application the MCU manages also the communication protocol i.e. the switching between transmit and receive mode, the preamble, the start byte, the bit encoding and decoding and other important operations.

## **Optional microboard**

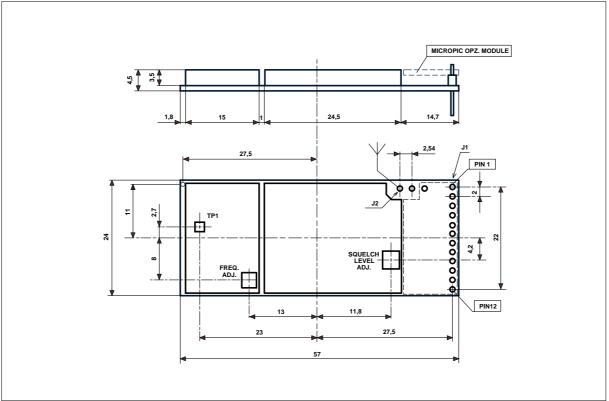

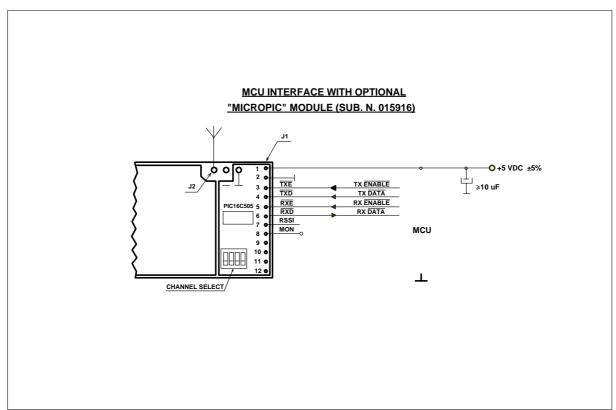

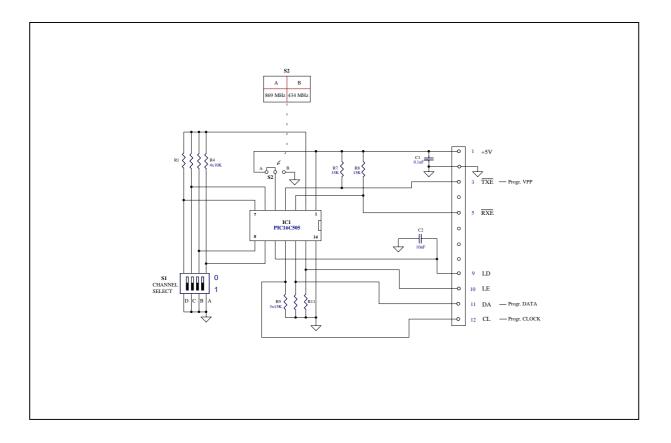

An optional small  $\mu C$  board ( Micropic Module – part.n° 015916) can be directly mounted on the transceiver J1 connector.

The Micropic Module eliminates the necessity of an external programming of Tx and Rx frequencies. Up to 16 factory pre-programmed RF channels can be easily selected by means of a four positions dip–switch.

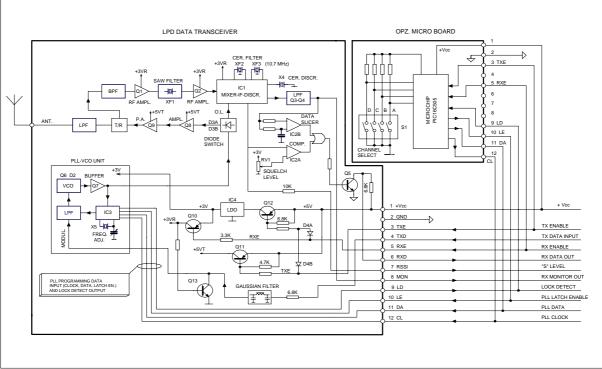

Fig.1 - Functional block diagram.

|                                                 | Min     | Тур   | Max          | Units | Notes |

|-------------------------------------------------|---------|-------|--------------|-------|-------|

| GENERAL                                         |         |       |              |       |       |

| FREQUENCY RANGE                                 | 432.000 |       | 436.000      | MHz   | (1)   |

| CHANNEL SPACING                                 | 150     | 200   |              | KHz   | ( )   |

| FREQUENCY PROGR. STEP                           | 25      | 50    | 100          | KHz   |       |

| FREQUENCY STABILITY                             |         | ±4    | ±7           | KHz   | (2)   |

| DATA RATE                                       | 7.2     |       | 64           | Kbaud |       |

| ANTENNA IMPEDANCE                               |         | 50    |              | Ω     |       |

| SUPPLY VOLTAGE                                  | 4.75    | 5     | 5.25         | V     |       |

| SUPPLY CURRENT - SLEEP                          | 4.75    | 1     | 10           | μA    |       |

| SUPPLY CURRENT - Rx MODE                        |         | 21    | 24           | mA    |       |

| SUPPLY CURRENT - TX MODE                        |         | 30    | 35           | mA    |       |

| OPERATING TEMPERATURE                           | - 20    | 00    | + 60         | °C    |       |

|                                                 |         |       |              |       |       |

| TRANSMITTER                                     |         |       |              |       |       |

| RF OUTPUT POWER                                 | 15      |       | 20           | mW    | (3)   |

| SPURIOUS EMISSION                               |         |       | - 50         | dBc   |       |

| MODULATION FREQUENCY                            | 3.5     |       | 32           | KHz   | (4)   |

| FM DEVIATION                                    |         | 30    |              | KHz   | (4)   |

| R/T SWITCHING TIME                              |         | 2     |              | ms    | (5)   |

| CHANNEL SWITCHING TIME                          |         | 1     |              | ms    | (5)   |

| RECEIVER                                        |         |       |              |       |       |

| SENSITIVITY                                     | - 102   | - 106 |              | dBm   |       |

| SELECTIVITY                                     |         | 40    | 30           | dB    | (6)   |

| IMAGE REJECTION                                 |         | 50    |              | dB    | ( 0 ) |

| DYNAMIC RANGE                                   |         | 100   |              | dB    |       |

| SQUELCH LEVEL ADJ. RANGE                        | - 115   | - 110 | - 70         | dBm   |       |

| T/R SWITCHING TIME                              |         | 1.5   |              | ms    | (5)   |

| CHANNEL SWITCHING TIME                          |         | 500   |              | μs    | (5)   |

| DIMENSIONS                                      |         | 57.)  | < 24 x 4.5 r | nm    |       |

| WEIGHT                                          |         | 0.7   | 10 g         |       |       |

| NOTE :                                          |         |       | 10 9         |       |       |

| (1) CEPT SRD BAND LIMITS = 433.05 – 434.79 I    | MHz     |       |              |       |       |

| (2) OVER OPERATING TEMPERATURE RANGE            |         |       |              |       |       |

| (3) POWER ON 50 $\Omega$ . CEPT MAX ERP = 10 mW |         |       |              |       |       |

| (4) SQUARE WAVE 0-5 Vdc LEVEL                   |         |       |              |       |       |

| (5) PLL LOCK-UP TIME                            |         |       |              |       |       |

| (6) AT Fo ± 200 KHz                             |         |       |              |       |       |

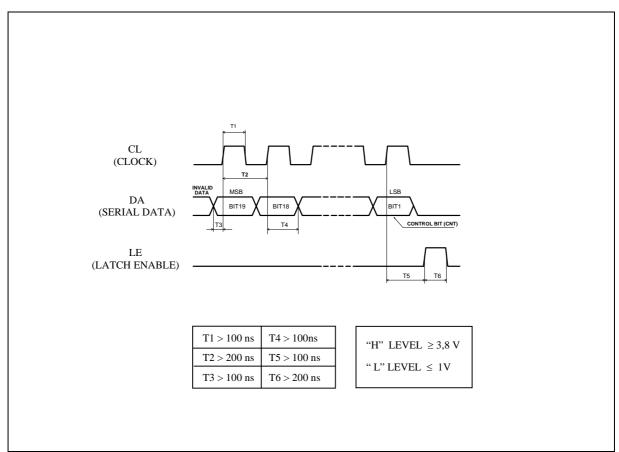

Fig. 3 - Timing diagram, serial interface.

Fig. 4 - J1 pin connections.

Fig. 5 - J1 pin connections

## Operating modes.

The BK67F5 has three main operating modes as set by the  $\overline{\text{TXE}}$  and  $\overline{\text{RXE}}$  input and illustrated in table below.

| MODE     | TXE | RXE | DESCRIPTION                             |

|----------|-----|-----|-----------------------------------------|

| SLEEP    | 1   | 1   | Quiescent current $< 1 \ \mu A$         |

| RECEIVE  | 1   | 0   | PLL and Receiver enabled Icc = 22 mA    |

| TRANSMIT | 0   | 1   | PLL and Transmitter enabled Icc = 40 mA |

When switched from one operating mode to another, the transceiver needs to receive, through the 3 wires serial interface, the appropriate frequency programming sets of bits.

#### Frequency programming.

1) <u>The "PLL" frequency synthesizer.</u>

Transmitter and receiver local oscillator (L.O.) frequencies are generated by a low phasenoise "VCO" (voltage controlled oscillator).

Figure 1 shows the block diagram of the transceiver.

IC3, a Fujitsu MB15E03SL, is the "PLL" integrated circuit that locks the "VCO" to the reference (X5 Xtal).

#### 2) <u>Serial control interface description.</u>

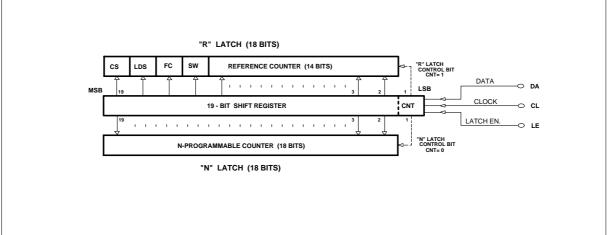

A 3 wires serial control interface (clock, data and latch enable) is used to program the "PLL" IC (see fig. 6). Data are written into the 19-bit shift register at the rising edge of the "CL" (clock) signal (MSB first).

Data are transferred then into the appropriate 18-bit latch at the rising edge of the "LE" (latch enable) pulse depending on the "CNT" (control bit ) value. "R" latch is loaded if "CNT" bit is set to "1", "N" latch is loaded with "CNT" = 0.

To program a Tx or Rx frequency, two control words 19-bit length must be written into the shift register: the "**R**" word and the "**N**" word.

Fig. 6 - PLL internal register and latches.

3) <u>PLL frequency synthesizer parameters</u>

| PLL IC<br>Reference frequency<br>Programming frequency step                                                                                                                              | <ul> <li>Fujitsu MB15E03SL</li> <li>16,8 MHz</li> <li>50 KHz (recommended)<br/>25-75-100 KHz (optional)</li> </ul>                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "SW" bit (bit 1-16 of "R" word) = 1<br>"FC" bit (bit 17 of "R" word) = 1<br>"LDS" bit (bit 18 of "R" word) = 0<br>"CS" bit (bit 19 of "R" word) = 1<br>"CS" bit (bit 19 of "R" word) = 0 | <ul> <li>PRESCALER divide ratio = 64/65</li> <li>PHASE comparator positive output</li> <li>LOCK-DETECT signal available</li> <li>CHARGE/PUMP curr. = 6 mA</li> <li>CHARGE/PUMP curr. = 1,5 mA</li> </ul> |

Note: Although these are the recommended parameters, different "PLL" programming modes can be implemented, if necessary. Refer to MB15E03SL data sheet at <u>www.fujitsumicro.com</u> for further information.

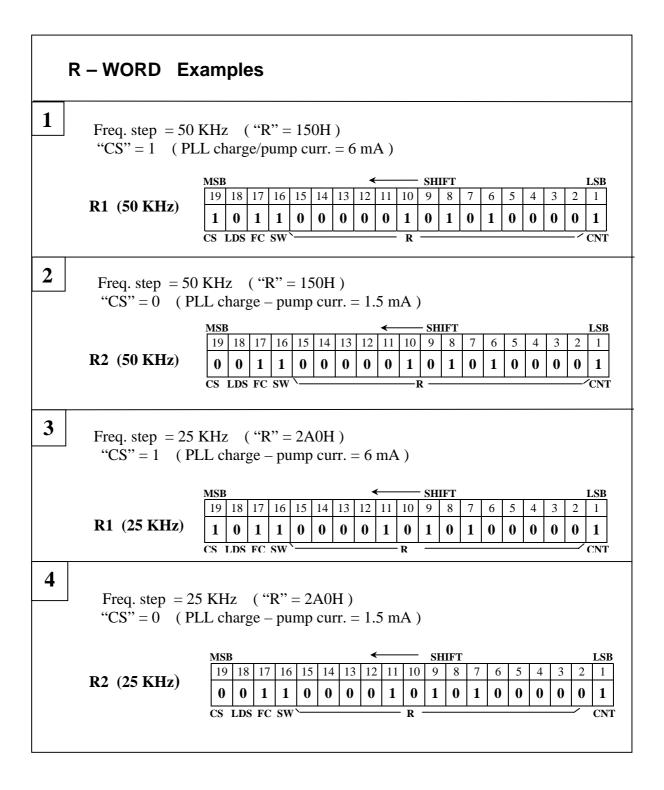

4) <u>R-word</u>

Bit 1 (CNT) must be set to "1". Bits from 2 to 15 are the "R" number Bits from 16 to 19 are the "SW", "FC", "LDS" and "CS" bits.

"R" is the value that is loaded into the PLL reference divider and is calculated dividing the reference frequency (16800 KHz) by the required minimum programming frequency step.

Ex.1 : for a 50 KHz freq. step

R = 16800 / 50 = 336 (150 H)

The "CS" bit is different from receive to transmit mode. In receive mode the "CS" bit is always "1". In transmit mode the "CS" bit must first be set to "1" (word "R1" fast PLL lock-up time) and then, after lock-up time, must be changed to "0" (word "R2"). For more information refer to the *timing diagrams* [pages 10 - 11].

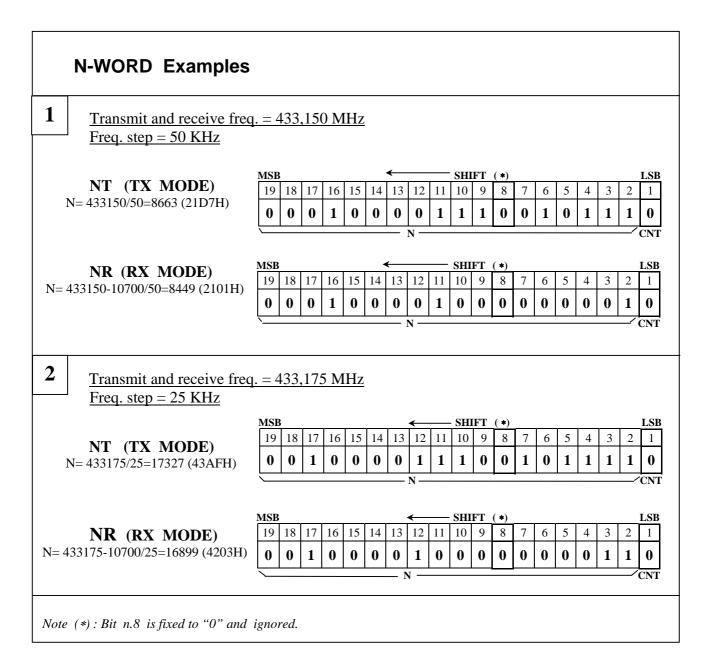

5) <u>N-word</u>

Bit 1 (CNT) must be "0". Bits from 2 to 19 are the "N" number.

"N" value is calculated dividing the "VCO" frequency by the frequency step. In transmission mode the VCO frequency is the transmit frequency . In receive mode the VCO frequency is the receive frequency minus the receiver IF (INTERMEDIATE FREQ. = 10700 KHz).

NOTE: Due to the internal architecture of the "PLL" IC, when "SW" bit of R-WORD (bit n. 16) is "1" (prescaler divide ratio = 64/65), bit n. 8 of N-word must not be used. It must be fixed to "0" and ignored.

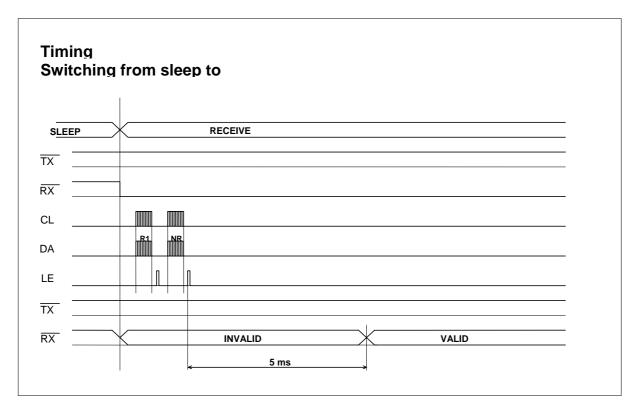

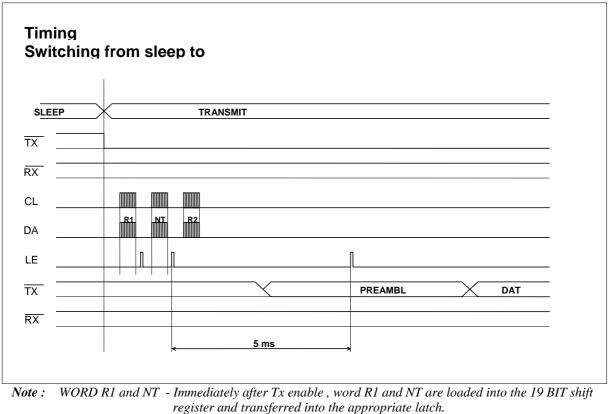

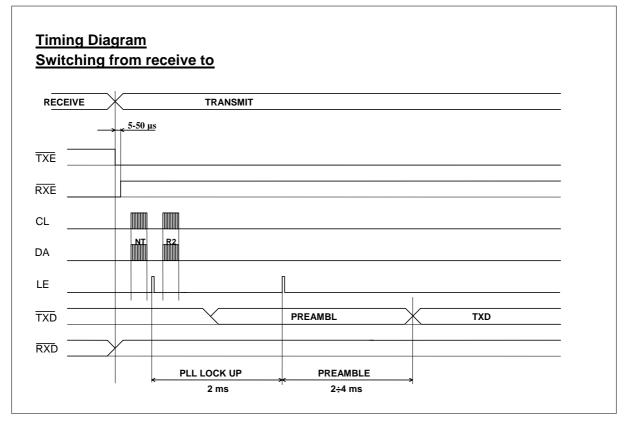

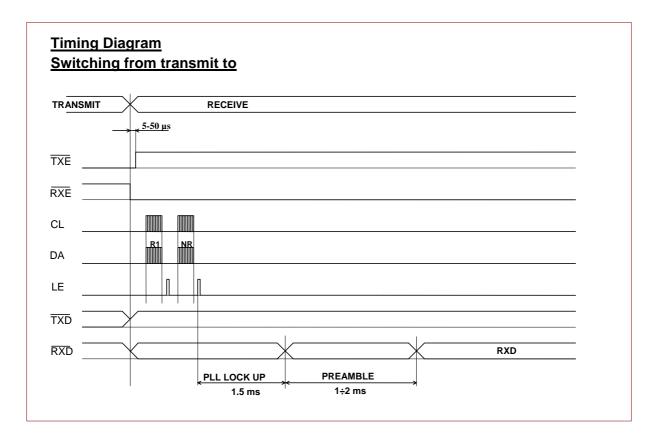

## TIMING DIAGRAMS

Switching between different operating modes

WORD R2 - V

R2 - Word R2 is loaded into the 19BIT shift register, but it is loaded into "R" latch only after PLL lock-up time.

*Note*: WORD NT - Immediately after Tx enable ( and Rx disable), word NT is loaded into the 19 BIT shift register and transferred into "N" latch.

WORD R2 - Word R2 is loaded into the 19 BIT shift register, but it is loaded into "R" latch only after PLL lock-up time.

## Transmitter data input $(T\overline{XD} - J1 \text{ pin n. 4})$ .

TXD input (negative logic) will accept serial digital data with a 0 V to 5 V level (for full Tx modulation ). Modulation shaping is performed by a Gaussian low pass filter to minimize spectral spreading (see fig. 1).

Bit-rate is upper limited by the cut-off frequency of the low-pass filter.

Minimum bit-rate depends on the "PLL" loop filter time constants and the value of "CS" bit ( R-word ). Minimum acceptable square wave modulation frequency is 3 KHz ( with "CS" bit = 0 ), DC levels or a data /streams with DC unbalance are prohibited.

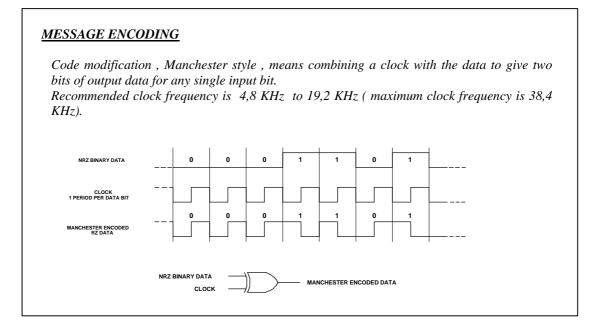

Bi-phase "RZ" coding schemes ( differential bi-phase or Manchester code ) are recommended to eliminate any DC component that depends on the bit pattern.

## Received data output (RXD - J1 pin n. 6).

RXD (negative logic) is an open collector output ( Q5 transistor – fig. 1) with a pull-up resistor to Vcc.

The received data stream demodulated by IC1 discriminator goes to a post detection low pass filter (Q3 - Q4) which limits the signal bandwidth and ensures the clean operation of the subsequent self-centering data slicer (IC2B).

A squelch circuit , blocks the RXD output when the received signal strenght falls a preset value (adjusted by RV1).

The squelch level is factory preset with to approx. 6 dB under max. sensitivity. RV1 can be adjusted to increase the squelch level threshold.

$This \ adjust ement \ is \ best \ performed \ in \ laboratory \ with \ a \ calibrated \ RF \ generator.$

It is also possible to adjust RV1 observing the received RF signal level on "RSSI" output .

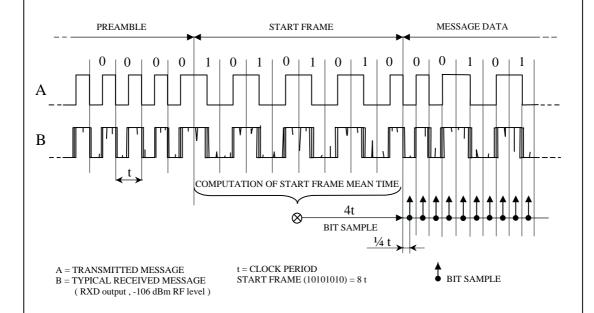

#### **MESSAGE DECODING**

On the receiver side, trasmitted (bi-iphase encoded) datas, must be extracted from noise, interference and multipath propagation distortions.

It is very instructive, before any decode attempt, to examine the received datas as appear on the "MON" analog output.

A good system is to employ as a beacon a transceiver module in transmit mode, modulated by a square-wave (clock frequency) and to simulate all the steady and transitory situations of a real message exchange.

Suppose transmitted data are Manchester encoded, as described in the previous example. It will be necessary to send a preamble, a syncronization frame and then the message.

The preamble is only to allow Tx and Rx to stabilize on the frequency and to centre modulation and data slicer.

The syncronisation frame is to be used to define start point for following bits decoding.

In the above example, if "t" is the clock period, the total length of the eight bits start frame (10101010) is "8t".

The start frame must be extracted from a noisy reception detecting the rising and falling edge of the received message.

Once extracted from the received noisy signal, the 8 bits of the start frame can be averaged on the total frame time to permit to define the data message start point. The following message data bits are best decoded sampling two times every bit.

- *Note: Obviously any tolerance in the Rx and Tx clock frequency must be taken in consideration and related to the total message bit number.*

- Control and validation of the message together with error correction algorithms, message retry request, etc. is a task to be performed by the "packet" protocol.

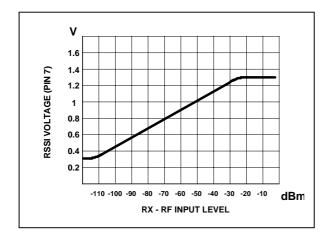

#### Received signal strenght indicator output (RSSI – J1 pin n. 7).

RSSI is a received signal strenght output with more than 90 dB dynamic range (fig. 7).

DBm to RF Volt conversion  $Zo = 50\Omega \quad 0 \text{ dBm} = 1 \text{ mV}$ dBm RF mV dBm  $RF \mu V$ -20 dBm -80 dBm 22,4 mV 22,4 µV 7,07 mV -90 dBm -30 dBm 7,07 µV -40 dBm 2,24 mV -100 dBm 2,24 µV 0,70 mV -50 dBm -110 dBm 0,7 µV -60 dBm 0,22 mV -120 dBm 0,22 µV -70 dBm 0.07 mV -130 dBm 0,07 µV

Fig. 7 - RSSI output.

The accurate "RSSI" output can be used to test and evaluate antenna performances and to measure radio waves propagation and attenuation.

#### Monitor analog Rx output (MON – J1 pin n. 8).

This is a direct analogue output from demodulator.

It is employed during receiver test, but it is also very useful during system test to observe (before shaping) the received signal. This will help to evaluate the signal to noise ratio and the signal distortion as for example influenced by radio waves propagation anomalies (multipath reflection).

The monitor output can also be of great help to detect and observe noise and interference sources (for example from micros, fast logic IC, noisy diodes or zeners etc.). A small loop at the end of a coaxial 50  $\Omega$  cable and connected to antenna input can help to measure and locate suspect noise sources.

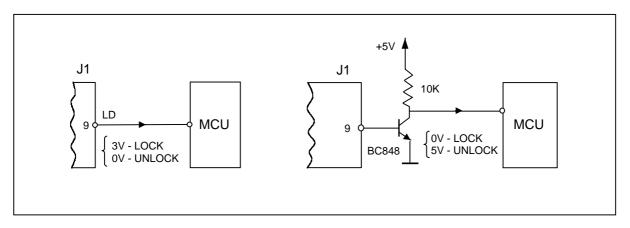

## Lock detect output (LD –J1 pin n. 9).

During normal operation, in receive or transmit mode , the "PLL" is locked to the correct programmed frequency and the LD output is high (+3 V).

Fig. 8 Lock detect output interface to MCU.

During normal operation, with short transmission and reception periods, it is not usually necessary to control the "UNLOCK" situation.

An "UNLOCK" situation is possible during a long period of continuos transmission ( usually prohibited) or reception : in this case the MCU detects the "UNLOCK" state and provides to resend the appropriate programming words.

*Note :* Avoid to sample the "LD" status immediately after the programming sequence. A time of 100 ms or more, also between subsequent "LD" controls, is recommended.

www.stecom.com

ste@stecom.com

## MICROPIC MODULE.

The optional Micropic Module can be directly mounted on BK67, BK68 and BK69 data transceiver.

The on board microcontroller (PIC16C505) programs the transceiver, through the serial data interface on 16 different radio channels as selected by S1 ( a four position dip – switch).

The microcontroller also samples every 100 ms the LD (lock detect) output to monitor the "PLL" status, reprogramming the transceiver in case of "unlock" event.

| TAI |            | ICROPIC MO | -       |             |             |                |    |    |    |                 |      |       |      |                       |   |   |   |     |     |                |     |    |     |      |      |     |    |    |      |     |           |      |   |   |     |     |   |   |

|-----|------------|------------|---------|-------------|-------------|----------------|----|----|----|-----------------|------|-------|------|-----------------------|---|---|---|-----|-----|----------------|-----|----|-----|------|------|-----|----|----|------|-----|-----------|------|---|---|-----|-----|---|---|

|     | BI         | K67F5 433, | 05 - 43 | 34,79 MHz I | SM BAND     | <b></b>        |    |    |    |                 |      |       |      |                       |   |   |   |     |     |                | :   | ᄀᄃ |     |      |      |     |    |    |      |     |           |      |   |   |     |     |   |   |

| CH. | DIP-SWITCH | FREQUENCY  | STE     | CHANNEL     | FREQUENCY   | NT WORD OFIXED |    |    |    |                 |      |       |      | NR WORD <u>OFIXED</u> |   |   |   |     |     |                |     |    |     |      |      | CNT |    |    |      |     |           |      |   |   |     |     |   |   |

|     |            |            | CH.     | SEPARATION  | PROGR. STEP |                |    |    |    |                 |      |       |      |                       | - |   |   |     | 1   | <del></del>    |     |    |     |      | -    | -   |    |    |      |     | <b></b> _ | 1    | - |   |     |     |   | - |

| N°  | DCBA       | MHz        | CODE    | KHz         | KHz         | 19             | 18 | 17 | 16 | 15 <sup>-</sup> | 14 1 | 13 12 | 2 11 | 10                    | 9 | 8 | 7 | 6 5 | 4   | 3              | 2 1 | 1  | 9 1 | 8 17 | 7 16 | 15  | 14 | 13 | 12 1 | 1 1 | 0 9       | 8    | 7 | 6 | 5 4 | 4 3 | 2 | 1 |

| 1   | 0000       | 433,150    | M1      | 200         | 50          | 0              | 0  | 0  | 1  | 0               | 0    | 0 0   | 1    | 1                     | 1 | 0 | 0 | 1 0 | 1   | 1              | 1 0 |    | 0   | ) 0  | 1    | 0   | 0  | 0  | 0    | 1 0 | ) (       | ) 0  | 0 | 0 | 0   | 00  | 1 | 0 |

| 2   | 0001       | 433,350    | M2      | ,,          | ,,          | 0              | 0  | 0  | 1  | 0               | 0    | 0 0   | 1    | 1                     | 1 | 0 | 0 | 1 1 | 0   | 1 <sup>·</sup> | 1 0 |    | D C | ) 0  | 1    | 0   | 0  | 0  | 0    | 1 0 | ) (       | ) 0  | 0 | 0 | 0 ′ | 10  | 1 | 0 |

| 3   | 0010       | 433,550    | М3      | ,,          | ,,          | 0              | 0  | 0  | 1  | 0               | 0    | 0 0   | 1    | 1                     | 1 | 0 | 0 | 1 1 | 1   | 1 <sup>·</sup> | 1 0 |    | 0   | ) 0  | 1    | 0   | 0  | 0  | 0    | 1 0 | ) (       | ) () | 0 | 0 | 1 ( | 0 0 | 1 | 0 |

| 4   | 0011       | 433,750    | M4      | ,,          | ,,          | 0              | 0  | 0  | 1  | 0               | 0    | 0 0   | 1    | 1                     | 1 | 0 | 1 | 0 0 | 0   | 1 <sup>·</sup> | 1 0 |    | 0   | ) 0  | 1    | 0   | 0  | 0  | 0    | 1 0 | ) (       | ) () | 0 | 0 | 1 ′ | 10  | 1 | 0 |

| 5   | 0100       | 433,950    | M5      | ,,          | ,,          | 0              | 0  | 0  | 1  | 0               | 0    | 0 0   | 1    | 1                     | 1 | 0 | 1 | 0 0 | 1   | 1 <sup>·</sup> | 1 0 |    | 0   | ) 0  | 1    | 0   | 0  | 0  | 0    | 1 0 | ) (       | ) () | 0 | 1 | 0 ( | 0 0 | 1 | 0 |

| 6   | 0101       | 434,150    | M6      | ,,          | ,,          | 0              | 0  | 0  | 1  | 0               | 0    | 0 0   | 1    | 1                     | 1 | 0 | 1 | 0 1 | 0   | 1 <sup>·</sup> | 1 0 |    | 0   | ) 0  | 1    | 0   | 0  | 0  | 0    | 1 0 | ) (       | ) () | 0 | 1 | 0 ′ | 1 0 | 1 | 0 |

| 7   | 0110       | 434,350    | M7      | ,,          | ,,          | 0              | 0  | 0  | 1  | 0               | 0    | 0 0   | 1    | 1                     | 1 | 0 | 1 | 0 1 | 1   | 1 <sup>·</sup> | 1 0 |    | 0   | ) 0  | 1    | 0   | 0  | 0  | 0    | 1 0 | ) (       | ) () | 0 | 1 | 1 ( | 0 0 | 1 | 0 |

| 8   | 0111       | 434,550    | M8      | ,,          | ,,          | 0              | 0  | 0  | 1  | 0               | 0    | 0 0   | 1    | 1                     | 1 | 0 | 1 | 1 0 | 0   | 1 <sup>·</sup> | 1 0 |    | 0   | ) 0  | 1    | 0   | 0  | 0  | 0    | 1 0 | ) (       | ) () | 0 | 1 | 1 ′ | 1 0 | 1 | 0 |

| 9   | 1000       | 434,750    | M9      | ,,          | ,,          | 0              | 0  | 0  | 1  | 0               | 0    | 0 0   | 1    | 1                     | 1 | 0 | 1 | 1 0 | 1   | 1 <sup>·</sup> | 1 0 |    | 0   | ) 0  | 1    | 0   | 0  | 0  | 0    | 1 0 | ) (       | ) () | 1 | 0 | 0 ( | 0 0 | 1 | 0 |

| 10  | 1001       | 433,175    | G1      | 250         | 25          | 0              | 0  | 1  | 0  | 0               | 0    | 0 1   | 1    | 1                     | 0 | 0 | 1 | 0 1 | 1   | 1 <sup>·</sup> | 1 0 |    | 0   | ) 1  | 0    | 0   | 0  | 0  | 1 (  | 0   | ) (       | ) () | 0 | 0 | 0 ( | 0 1 | 1 | 0 |

| 11  | 1010       | 433,425    | G2      | ,,          | ,,          | 0              | 0  | 1  | 0  | 0               | 0    | 0 1   | 1    | 1                     | 0 | 0 | 1 | 1 1 | 0   | 0              | 1 0 |    | 0   | ) 1  | 0    | 0   | 0  | 0  | 1 (  | 0   | ) (       | ) () | 0 | 0 | 1 ′ | 10  | 1 | 0 |

| 12  | 1011       | 433,675    | G3      | ,,          | ,,          | 0              | 0  | 1  | 0  | 0               | 0    | 0 1   | 1    | 1                     | 1 | 0 | 0 | 0 0 | 0   | 1 <sup>·</sup> | 1 0 |    | D   | ) 1  | 0    | 0   | 0  | 0  | 1    | 0   | ) (       | ) 0  | 0 | 1 | 0 1 | 1 1 | 1 | 0 |

| 13  | 1100       | 433,925    | G4      | ,,          | ,,          | 0              | 0  | 1  | 0  | 0               | 0    | 0 1   | 1    | 1                     | 1 | 0 | 0 | 0 1 | 1   | 0              | 1 0 |    | 0   | ) 1  | 0    | 0   | 0  | 0  | 1    | 0   | ) (       | ) 0  | 1 | 0 | 0   | 00  | 1 | 0 |

| 14  | 1101       | 434,175    | G5      | ,,          | ,,          | 0              | 0  | 1  | 0  | 0               | 0    | 0 1   | 1    | 1                     | 1 | 0 | 0 | 1 0 | ) 1 | 1              | 1 0 |    | 0   | ) 1  | 0    | 0   | 0  | 0  | 1    | 0   | ) (       | ) 0  | 1 | 0 | 1 ( | 0 1 | 1 | 0 |

| 15  | 1110       | 434,425    | G6      | ,,          | ,,          | 0              | 0  | 1  | 0  | 0               | 0    | 0 1   | 1    | 1                     | 1 | 0 | 1 | 0 0 | 0   | 0              | 1 0 |    | 0   | ) 1  | 0    | 0   | 0  | 0  | 1    | 0   | ) (       | ) 0  | 1 | 1 | 0 ′ | 1 0 | 1 | 0 |

| 16  | 1111       | 434,675    | G7      | ,,          | ,,          | 0              | 0  | 1  | 0  | 0               | 0    | 0 1   | 1    | 1                     | 1 | 0 | 1 | 0 1 | 0   | 1 <sup>.</sup> | 1 0 |    | 0   | ) 1  | 0    | 0   | 0  | 0  | 1    | 0   | ) (       | 0    | 1 | 1 | 1 1 | 1 1 | 1 | 0 |

- 6

#### Antennas.

In transmission the antenna allows RF energy to be efficiently radiated into free space.

Note 1 : the BK6X output RF power is purposefully set higher than the legal limit. This allows to utilize a poor efficiently antenna to radiate max legal power.

In reception the antenna intercepts the electromagnetic RF field ( an equivalent capture area is definied for every antenna ) and sends the resulting weak current to the receiver input.

- Note 2 : the receiving antenna should capture as much of the transmitted signal as possible and as little as possible of other undesired signals.

- Note 3 : it is useless to have a high RX sensitivity and the good antenna located very near to disturbing sources like fast logic circuits, switching power regulators, etc.

There are hundreds of antenna styles and variations that may be employed (dipole, whip, helical, spiral, loop, patch, etc.) but the simplest and most popular antenna is the quarter wavwlenght whip antenna (ground-plane antenna).

Basically the ground-plane "whip" antenna is quarter wavelenght wire that stands above ground-plane.

This antenna is very simple to design and to manufacture, but to be succesfull it is necessary to match two conditions:

- 1°) The wire (yhe radiating element) must stand right in poen space, perpendicular to ground-plane and far away from conductive obstacles (metal parts walls etc.).

- 2°) The ground-plane must be really "ground", i.e. it must have enough extension compared to wavelenght to be really "zero" equipotential ground.

- Note 4 : the ground-plane antenna has (at resonance frequency) nominal impedance of 36  $\Omega$ , which is close enough to standard 50  $\Omega$  impedance.